Fully interrupt driven soft-uart receiver

Preparations for brain surgery

Preparations for brain surgery

OLS - UART decoding

OLS - UART sniffing

Openbench logic sniffer

OLS - UART sniffing

Testing the soft-uart receiver on an ATtiny24

Fully interrupt driven soft-uart receiver on an AT…

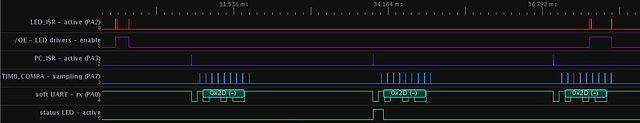

Optimized ISR runtime - 8th pulse

Optimized sampling-ISR runtime

Optimized ISR runtime - 1st pulse

1st optimization attempt - 8th pulse

1st optimization attempt - 1st pulse

1st optimization attempt

Starting values - 8th pulse

Starting values - 1st pulse

Starting values - overview

Openbench logic sniffer - pull-up/down wing - Rev…

Openbench logic sniffer - pull-up/down wing - Rev…

OLS pull-up/down wing

OLS pull-up/down wing

OLS pull-up/down wing

Openbench logic sniffer - pull-down wing - Rev 0.1

Openbench logic sniffer - pull-down wing - Rev 0.1

OLS pull-up/down wing

OLS pull-up/down wing

Sniffing SPI traffic - RLE enabled

Sniffing SPI traffic - RLE enabled

Sniffing SPI traffic - RLE enabled

Keywords

Authorizations, license

-

Visible by: Everyone -

All rights reserved

-

87 visits

Fully interrupt driven soft-uart receiver

By accident I stumbled across my 'system-ticker' interrupt today. As it happens it conveniently ticks at 1MHz! One tick of timer0 is one microsecond. Microsecond timing is exactly what is needed for receiving serial data.

The sampling interrupt (TIM0_COMPA_vect) is now invoked at the right time by setting OCR0A = TCNT0 + FULL_BIT_DELAY.

The sampling interrupt (TIM0_COMPA_vect) is now invoked at the right time by setting OCR0A = TCNT0 + FULL_BIT_DELAY.

- Keyboard shortcuts:

Jump to top

RSS feed- Latest comments - Subscribe to the comment feeds of this photo

- ipernity © 2007-2024

- Help & Contact

|

Club news

|

About ipernity

|

History |

ipernity Club & Prices |

Guide of good conduct

Donate | Group guidelines | Privacy policy | Terms of use | Statutes | In memoria -

Facebook

Twitter

Sign-in to write a comment.